计组期末

第三章

加减指令执行后标志位的变化

过程调用的执行步骤、指针变化、入口参数(综合考)

数组访问

第五章 程序的执行

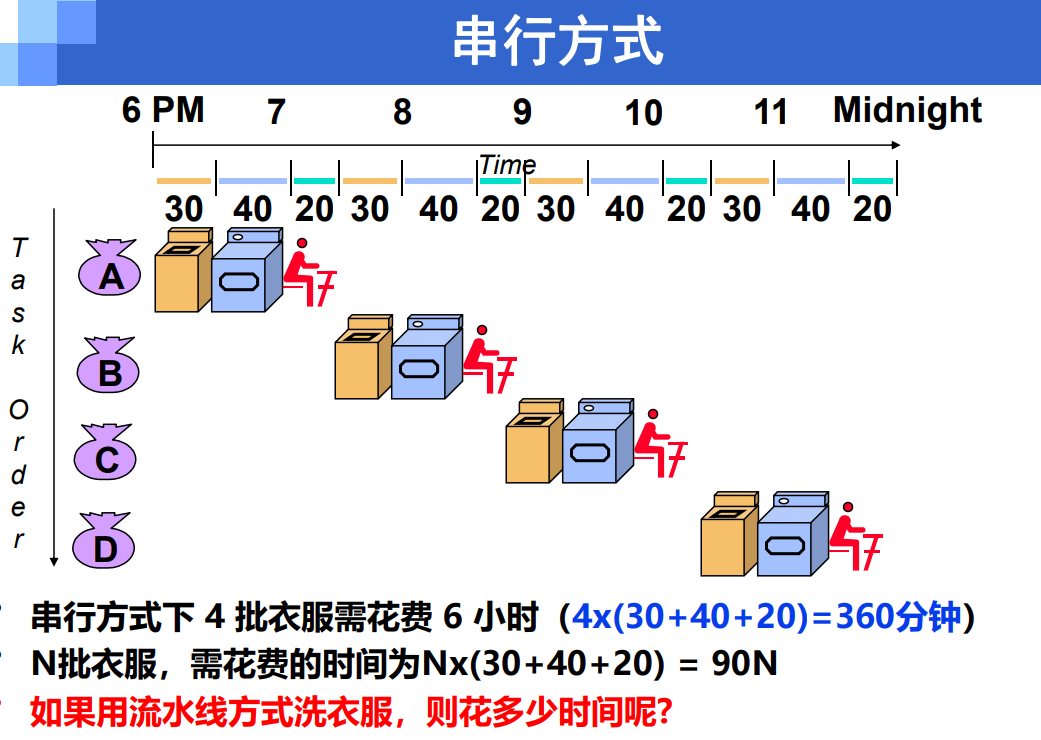

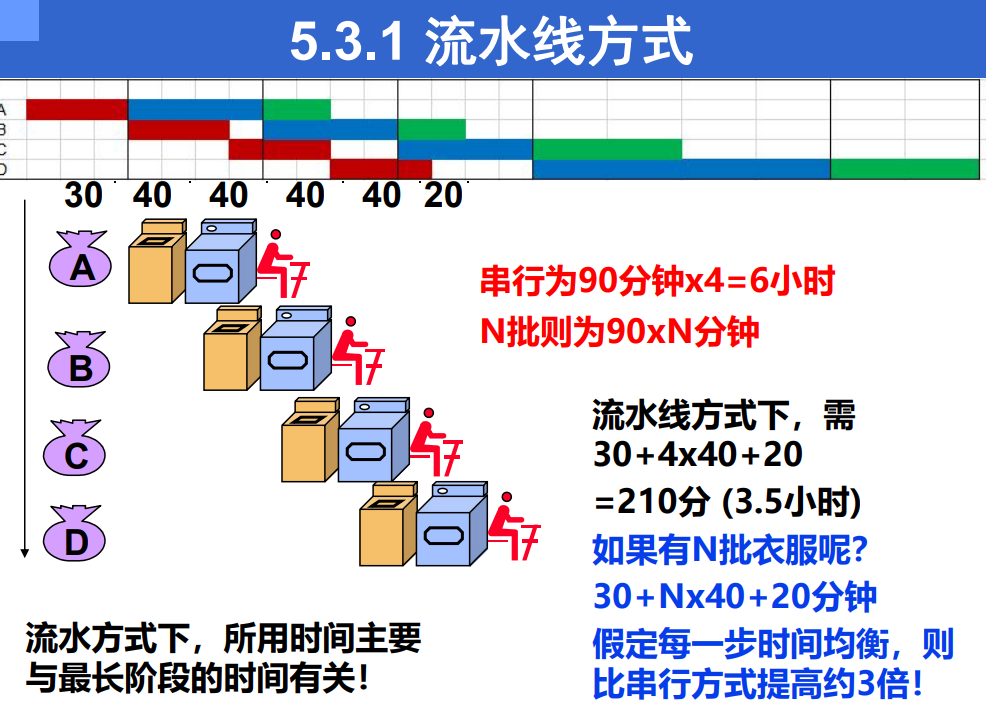

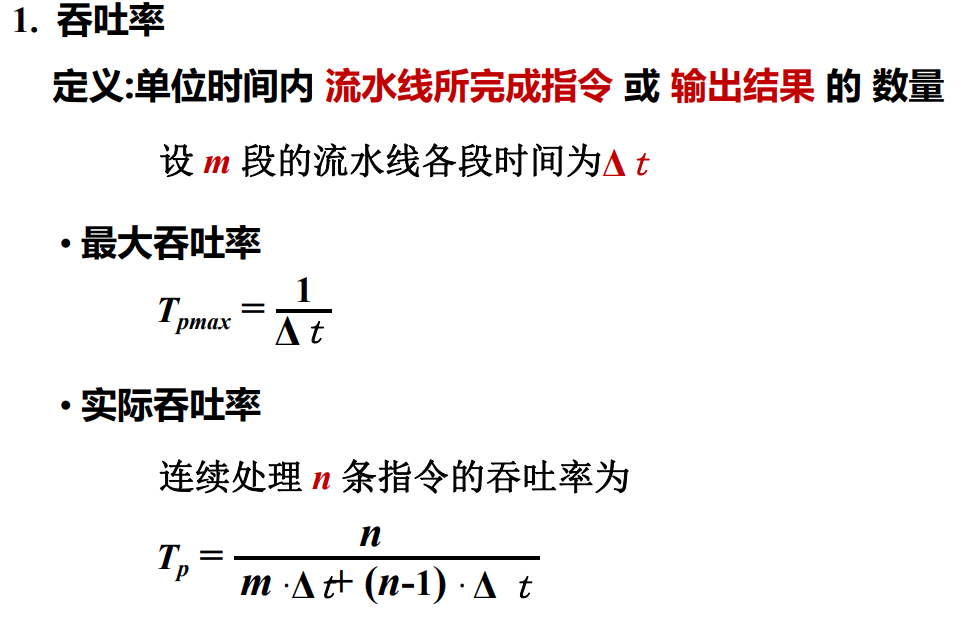

流水线技术:计算非流水线和流水线下指令执行的时间、吞吐率(应用)

五段流水线:

- 取指令(IF):根据PC的值从存储器取出指令

- 指令译码(ID):产生指令执行所需的控制信号

- 取操作数(OF):读取存储器操作数或寄存器操作数

- 执行(EX):对操作数完成指定操作

- 写回(WB):将操作结果写入存储器或寄存器

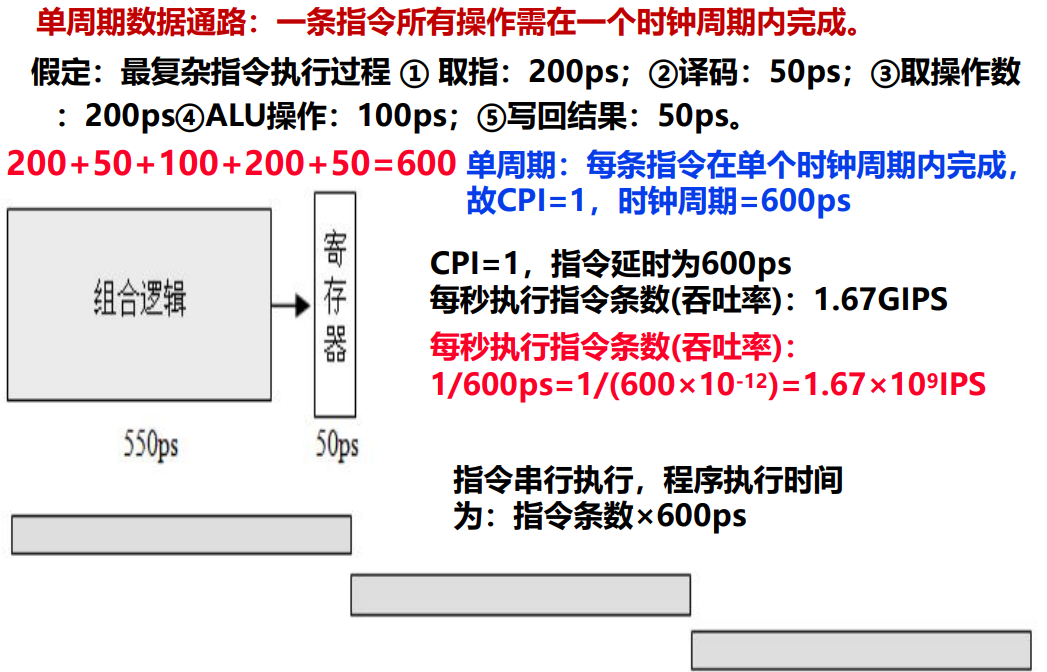

单周期数据通路

流水线数据通路

1ns=1000ps

1GIPS=1*10^9

流水线方式不一定缩短一条指令的执行。

流水线划分的越均匀越好。在比较均匀的情况下可以大大提高吞吐率。

指令流水段个数以最复杂指令所用的功能段个数为准;流水段的长度以最复杂功能段的操作时间为准。

什么样的指令集有利于流水线执行?

- 长度尽量一致,有利于简化取指令和指令译码操作

- MIPS指令32位,下址计算方便:PC+4

- X86指令从1字节到17字节不等,使取指部件及其复杂

- 格式少,且源寄存器位置相同,有利于在指令未知时就可取操作数

- MIPS指令的rs和rt位置一定,在指令译码时就可读取rs和rt的值

- 若位置随指令不同而不同,则需先确定指令类型才能取寄存器编号

- load/Store指令才能访问存储器,有利于减少操作数,规整流水线

- 内存中“对齐”存放,有利于减少访存次数和流水线的规整

总之,规整、简单和一致等特性有利于指令的流水线规划

精简指令集、复杂指令集的特点

精简指令集计算机(CISC):

- 指令系统复杂

- 指令周期长

- 各种指令都能访问存储器

- 采用微程序控制

- 难以进行编译优化来生成高效目标代码

缺陷:日趋庞大的指令系统不但使计算机的研制周期变长,而且难以保证设计的正确性,难以调试和维护,并且因指令操作复杂而增加机器周期,从而降低了系统性能

复杂指令计算机(RISC):

- 指令少

- 简化的指令系统

- 以RR方式工作

- 采用指令流水线技术,大部分指令在一个时钟周期内完成

- 采用大量通用寄存器,以减少访存次数

- 采用硬件连线控制器,不用或少用微程序控制

- 实现细节对机器级程序可见

吞吐率 流水线的性能指标

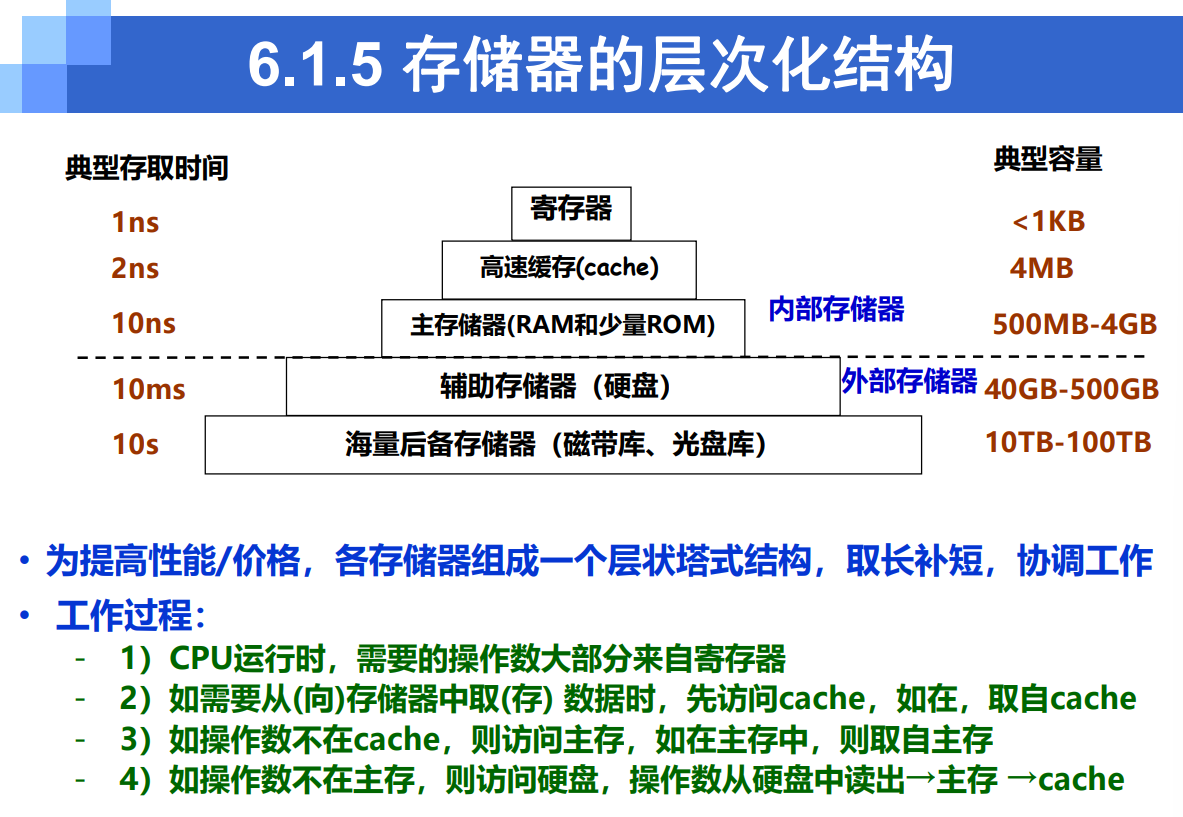

第六章 层次结构存储系统

存储器分类

按存取方式分类

- 随机存取存储器(RAM)

- 特点:按地址访问存储单元,每个单元读写时间一样。如:内存

- 顺序存取存储器(SAM)

- 特点:信息按顺序存放和读出,其存取时间取决于信息存放位置。如:磁带

- 直接存取存储器(DAM)

- 直接定位到读写数据块,在读写数据块时按顺序进行。如磁盘

- 相联存储器(AM、CAM)

- 按内容检索到存储位置进行读写。如快表

按断电后信息的可保存性分类

- 非易失性存储器

- 信息可一直保留,不需电源维持。如ROM、U盘、磁表面存储器、光存储器等

- 易失性存储器

- 电源关闭时信息自动丢失。如RAM、Cache等

基本概念区分

- 记忆单元(存储基元/存储元/位元/Cell)

- 具有两种稳态的能够表示二进制数码0和1的物理器件

- 存储单元(编址单元/超元)

- 具有相同地址的位构成一个存储单元,也称为编址单元

- 存储体(存储矩阵/存储阵列)

- 所有存储单元构成一个存储体

- 编址方式

- 字节编址、按字编址

- 存储器地址寄存器(MAR)

- 用于存放主存单元地址的寄存器

- 存储器数据寄存器(MDR)

- 用于存放主存单元中的数据的寄存器

层次化结构

引脚复用技术

- 减少芯片的地址引脚数,从而减小体积

- 在行选通信号RAS和列选通信号CAS的控制下,分时传送行、列地址

主存的扩展(应用)

- 位扩展

- 用若干片位数较少的存储器芯片构成给定字长的内存条时,需要进行位扩展

- 字数不变,位数扩展

- 字扩展

- 位数不变、扩充容量

- 字、位同时扩展

- 当芯片在容量和位数都不满足存储器要求的情况下,需要对字和位同时扩展

磁盘的相关概念

磁头:每个盘片的两面各有一个磁头,因此磁头号就等于盘面号

磁区:每个磁道被分为若干个磁区,以扇区为单位进行磁盘读写

磁道:磁头和盘片相对运动形成的圆构成一个磁道

柱面:多个盘片上相同的磁道形成一个柱面

外存平均响应时间/存取时间(应用)

响应时间=排队延迟+控制器时间+寻道时间+旋转等待时间+数据传输时间

存取时间=寻道时间+旋转等待时间+数据传输时间

平均存取时间=平均寻道时间+平均旋转等待时间+数据传输时间

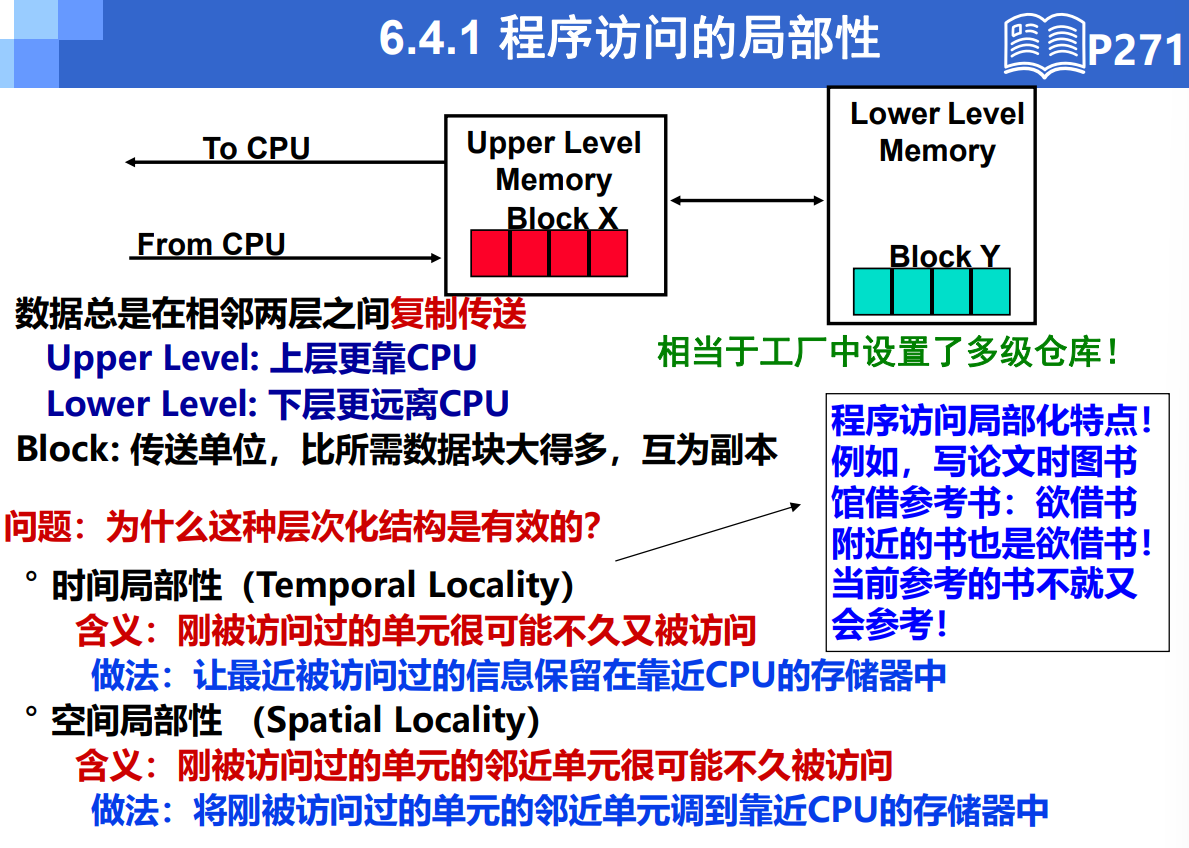

程序访问局部性原理会判别

命中率

命中(Hit):CPU访问单元所在块在Cache中

命中率(Hit Rate):在Cache中命中的概率,命中次数与总访问次数之比

命中时间(Hit Time):命中时,CPU在Cache直接存取信息,所用的时间开销

不命中(Miss):COU访问单元所在块不在Cache中

缺失率:1-(Hit Rate)

Cache映射方式(应用)

- 直接(Direct):每个主存块映射到Cache的固定行

- 全相联(Full Associate):每个主存块映射到Cache的任一行

- 组相联(Set Associate):每个主存块映射到Cache固定组中任一行

计组期末

http://cdt3211.github.io/2023/12/22/计组期末/